Interrupts on the IRQ input can be masked if the main program is doing something that you don't want interrupted right then for some reason. SEI SEts the Interrupt-disable bit (I) in the processor status register (P) so the IRQ pin will be ignored. When you're ready for interrupts again, use CLI to CLear the Interrupt-disable bit.

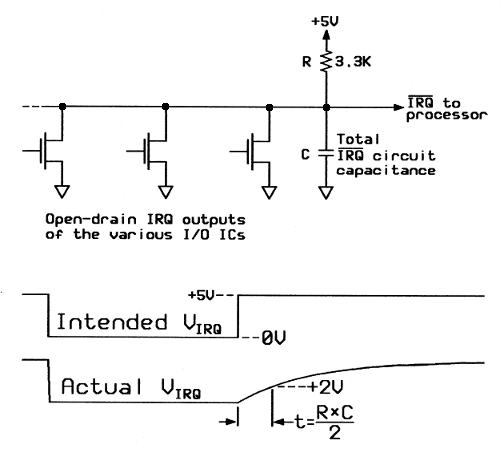

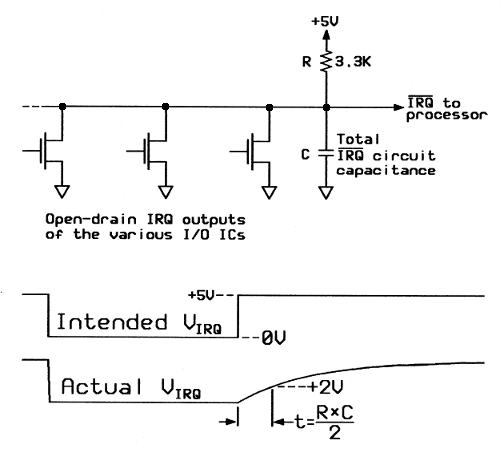

Most interrupts would come in on the IRQ input. Many of the 65-family I/O ICs have open-drain interrupt outputs so they can all go to the microprocessor by the same wire. This is a "wire-OR" logic and you'll need a pull-up resistor to bring the IRQ line high (meaning false) when nothing is pulling it down. 3KΩ is usually recommended in the data books. 3.3K is a standard 5% (and even 10%) value and is close enough.

For programming, note that there's a rather slow rise time with the pull-up resistor and the small but inevitable capacitance on the line, so it is good to clear the IC's interrupt condition early in your interrupt-service routine (ISR) to make sure the line has had time to float up before you reach the RTI and the processor status register is restored with the interrupt-disable bit clear. At low clock speeds you won't have trouble; but turn it up later and it can be a problem. I've been bit by it.

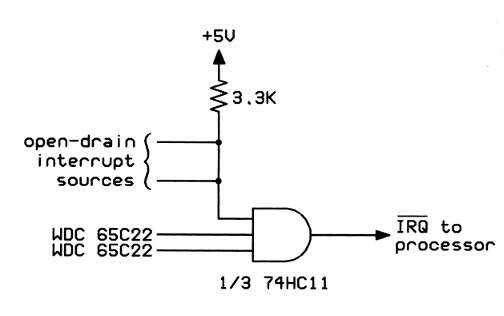

To remedy this, WDC's W65C22S's (note the "S" on the end) IRQ output is not open-drain, but a standard totem-pole output. This makes the rising edge much faster, which becomes important at the higher clock speeds. The down side to having the totem-pole IRQ outputs on WDC's W65C22S is that you need an AND-gate arrangement to connect two or more IRQ sources to the 6502's single IRQ input.

An AND-gate substitute would be to put a Shottky diode in series with each WDC W65C22S's IRQ output, with the cathode toward the WDC W65C22S, and connect the anodes together to the IRQ input on the processor with a single 3.3K pull-up resistor. This goes back to the rising-edge speed problem though; so I don't recommend it for the higher clock speeds of 5-10MHz and up.

It would have to be a very high priority to justify bringing an interrupt request in on the NMI input, and even then you normally would only have one source that can produce a falling edge on that input. Since it's non-maskable, multiple edges in quick succession could produce a situation where interrupts are interrupting already-started ISRs before they're done. If it's not intentional and under control, it could be a problem.

The only thing I have used NMI for regularly is a software time-of-day clock, where a counter in a 65c22 VIA produces an interrupt 100 times per second. I don't normally need it for telling what time of day it is, but it gets used to time things like key debounce, delay before key repeat, key repeat rate, and scheduled jobs without resorting to delay loops that would keep the processor from being able to do other things while waiting. A few jobs have required telling the 65c22 to stop the time-of-day clock interrupts on NMI so I could get better response time on the IRQ from another source without the jitter. (These have used up to 125,000 interrupts per second on the IRQ input.) I also have an "Abort" button and de-bounce circuit connected to the CA1 input of the same VIA, to get control back from a crashed program. It's similar to pushing the Reset button, but less drastic, as it does not reset all the hardware, only make the processor get out of the crashed program and start over.

Many designers will tell you the NMI should be reserved for warning of imminent power failure. However in most systems, the fraction of a second that the power supply takes to ramp down (if it matters at all) isn't enough time to do anything significant like store data to disc or even to a flash memory. The non-maskable interrupt doesn't have to be something terrible, analogous to the house being on fire. It could also be for something good, good enough to drop everything else!

If you're not sure which 6502 interrupt input you want a peripheral IC connected to, you might use a pin header to make it selectable later by putting the shorting jumper on the appropriate pair of pins. A DIP switch could be used, but takes more room. Again— just remember that you'll have to take extra precautions if you have more than one source at a time connected to the NMI since it is edge-triggered and not level-sensitive.

If you don't need to connect anything to the processor's interrupt input pins yet, just connect each one to Vcc through the 3.3K resistor.

I have a much more complete primer on interrupts

here. Enjoy my outdated cartoons!

memory map requirements <--Previous | Next--> 74 families & timing

last updated Feb 28, 2015